# LOAD-INTERACTIVE STEERED-INDUCTOR DC-DC CONVERTER WITH MINIMIZED OUTPUT FILTER CAPACITANCE

S. M. Ahsanuzzaman<sup>1</sup>, Amir Parayandeh<sup>1</sup>, Aleksandar Prodić<sup>1</sup>, Dragan Maksimović<sup>2</sup> <sup>1</sup>. ECE Department, University of Toronto, Toronto, CANADA <sup>2</sup>. ECEE Department, University of Colorado at Boulder, USA

Abstract- The paper introduces a concept of loadinteractive digitally controlled point-of-load (POL) dc-dc converters where the size of the output filter capacitor can be minimized based on the enhanced load-related communication between the digital load and the converter controller. Based on the information about upcoming load changes, the inductor current of the dc-dc converter is adjusted such that the converter output current matches the new load, thus minimizing the energy storage requirements for the output filter capacitor. The effectiveness of this approach is verified on a digitally controlled 3.3 V/ 30 W experimental prototype, where the dc-dc converter is a steered-inductor non-inverting buckboost. Transient response results show that, compared to standard converters with near-time optimal control, the new system has about three times smaller voltage deviation, allowing for a proportionally significant reduction in the output capacitor size.

## I. INTRODUCTION

In recent years, advanced "power aware" digital chipsets have been introduced in devices such as cell phones, computers, and other electronic equipment having a large portion of digital hardware. These digital loads communicate with power supplies and, to a certain extent, regulate their operation to reduce the overall power consumption [1-4]. Examples dynamic/adaptive include voltage scaling (DVS/AVS) and adaptive body biasing (ABB) techniques, where the supply voltage of the digital signal processors is dynamically changed, depending on the processing load, to minimize dynamic and static power consumption [1-6]. Also, the latest Intel chipsets, provide the switched-mode power supply (SMPS) with an indication of the current demand it expects over a period of time [7], so that this information can be used for phase shading that improves efficiency of multiphase SMPS, as shown in [8]. Methods that dynamically perform efficiency optimization of a segmented power stage based on the prediction of the load current from a digital signal stream processed by the electronic load have also been shown [9]. So far, communication between the digital load and the SMPS, has mostly been motivated by power savings.

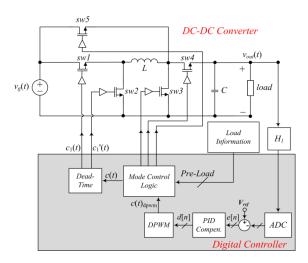

The objective of this paper is to show how this interaction can further be utilized to minimize the overall size of the SMPS, by dramatically reducing bulky and costly energy storage output filter capacitors. The novel system of Fig.1 consists of a modified non-inverting buck-boost converter, i.e. steered-inductor buck-boost, a digital controller, and a communication block providing load current information.

The modified buck-boost converter has an additional switch  $SW_5$ , for current steering [12], which, as it will be shown here, provides dramatic improvements of transient response in both buck and boost modes. It should be noted that the non-inverting buck boost is a common stage in numerous battery powered applications (e.g. [15]), so compared to those systems, no additional switches or conduction losses are introduced.

To provide the load current information, i.e. *pre-load* command, a block similar to those implemented in the latest generation of Intel processors [7] is used. Based on the *pre-load* command, during heavy-to-light load transients, the power stage is reconfigured, to steer the inductor current away from the output capacitor into the source. Similarly, the load information is used during the light-to-heavy transient to ramp up the inductor current to the upcoming load value before the transient occurs.

Fig.1: Digital Controller with modified buck-boost converter

This work has been supported by the Natural Science and Research Council of Canada (NSERC)

#### II. PRINCIPLE OF OPERATION

In a point-of-load (POL) dc-dc converter, the bulky output filter capacitor is sized based on the energy storage required to supply current during large step-load transients. This capacitor size is usually significantly larger compared to the size required to meet the output voltage ripple specification. The latency in the inductor current change, i.e. its limited slew rate, compared to that of the load is the major factor in determining the value of the output filter capacitance.

The converter of Fig. 1 is a modification of the steeredinductor topology proposed in [12]. This topology also resembles the conventional non-inverting buck boost converter [13], except for an addition of  $SW_5$ . This switch allows flexible and bidirectional control over the slope of the inductor current, which, in conjunction with the load information communicated by the load, as described in the following subsections, is a key element in providing dramatic improvements in the dynamic response. In the buck mode,  $SW_4$  is on,  $SW_3$  is off at all times while  $SW_1$  and  $SW_2$  change their states at the switching rate. When operating as a boost,  $SW_1$  is on,  $SW_2$  is off at all times and switches  $SW_3$  and  $SW_4$  are active.

It should be noted that constant operation in buck-boost mode (instantaneous conduction of  $SW_1$  and  $SW_3$  followed by the conduction of  $SW_2$  and  $SW_4$ ), is also possible. In this case, it is avoided in steady state operation, to minimize the number of active switching components operating at switching frequency and, consequently, to reduce the switching losses. Furthermore, in the buck mode, the rms current and consequently, the conduction losses, are also reduced.

#### A. Light-to-Heavy Load Transient Improvement

When operating as a conventional buck, the rate of change of the inductor current during a light-to-heavy load transient is limited by:

$$\frac{di_L}{dt} = \frac{V_g - V_{out}}{L} \tag{1}$$

where  $V_g$  is the input voltage,  $V_{out}$  is the output voltage and L is the converter inductance. As a result, during a sudden light-to-heavy load change, the output capacitor initially discharges providing the difference between the load and output currents, until the inductor current reaches the load value.

In the boost mode, when the input voltage is relatively low (compared to that of the output), the slope of the inductor current during a light-to-heavy load transient is limited by

$$\frac{di_L}{dt} = \frac{V_g}{L} \tag{2}$$

which causes a latency in the following of the load current. Moreover, to respond to a load transient, a fast acting controller initially disconnects the inductor from the load, leaving the output capacitor to provide all the current. In a properly designed SMPS, this capacitor is usually selected to

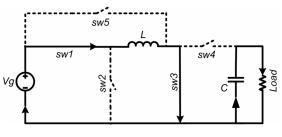

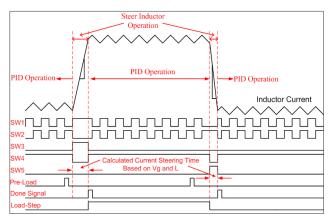

Fig.2 Light-to-Heavy Steer Inductor Operation

be large enough, so that the charge lost during transients does not significantly affect the output voltage.

In the system introduced here, the converter switches in the steering/boost mode of operation, based on a pre-load command. In this mode  $SW_1$  and  $SW_3$  are conducting to increase the inductor current. In some cases, this action is periodically replaced with the conduction of switches  $SW_1$  and  $SW_4$  to maintain the output voltage regulation, as described in the following section. During the steering/boost mode, the controller increases the inductor current to the load level prior to the load change, such that, ideally, at the transient instant, the two currents are matched. This results in a minimum amount of charge supplied by the capacitor. As shown in Fig.2, during the pre-charge phase, the inductor current is charged at the maximum instantaneous rate equal to  $V_g/L$ .

# B. Heavy-to-Light Load Transient Improvement

During a heavy-to-light load transient the inductor current slew rate of the buck converter is limited by:

$$\frac{di_L}{dt} = \frac{-V_{out}}{L} \tag{3}$$

In modern low power devices, where the output voltage of the converter is often very low (0.8-1.2V) [14], this limit severely slows down recovery from heavy-to-light load transients causing the output voltage overshoots. To minimize the overshoots, in a conventional converter, the output filter capacitor must be oversized.

In a traditional boost the situation is similar; the slope of the inductor current, limited by

$$\frac{di_L}{dt} = \frac{V_g - V_{out}}{L}$$

(4)

causes the capacitor overcharge. This is a significant problem when the difference between the input and output voltage of the converter is small, which is often the case in numerous portable applications, where a non-inverting buck-boost is used to slightly boost the battery voltage [16].

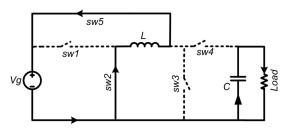

Unlike the light-to-heavy load transient operation that requires charging up the inductor current prior to the load transient, the heavy-to-light load operation is performed at the point when the actual load transition occurs. At that instant, the controller closes  $SW_2$  and  $SW_5$ , as shown in Fig. 3, to discharge the inductor current to the new steady state value while driving the current back to the source. It can be seen that this action not only disconnects the inductor from the capacitor and prevents overcharging but, in the buck mode,

Fig.3 Heavy-to-Light Steer Inductor Operation

also changes the current slew rate to a significantly higher value:

$$\frac{di_L}{dt} = \frac{-V_g}{L} \tag{5}$$

In this case, the preload command supplies the controller with the information about the new steady state current value, which is used to determine the point when the regular buck or boost operation could resume.

#### III. PRACTICAL IMPLEMENTATION

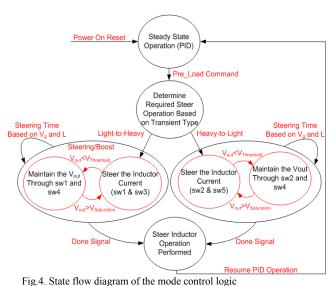

The controller architecture, shown in Fig.1, incorporates PID compensator that is used for steady-state voltage regulation with a block named *mode control logic*. The mode control logic is a finite state machine (FSM), which chooses different operating modes for the converter, depending on the pre-load information and the conditions in the circuit.

The state transitions of the FSM are shown in Fig. 4. During the steady state, a modified PID controller operates the converter as a buck or a boost, depending on the input and output voltages (as in [17]). Once the 'Pre-Load' command is received, the mode control logic determines the required steer-inductor current action. In the case of a light-to-heavy load transient, *steering/boost* is activated prior to the occurrence of the load step, to achieve the required inductor current. Once the desired current is reached, the FSM generates the 'Done Signal' to inform the load that the power consumption can be increased. In the case of the heavy-to-light load transient, *SW*<sub>2</sub> and *SW*<sub>5</sub> are turned on to steer the inductor current back to the source  $V_{g}$ .

Fig.5 demonstrates the operation of the mode control logic. The logic governs the inductor current steering after receiving the 'Pre-Load' command during steady state. Once the operation is completed the "Done Signal" is created to inform the load that the inductor current has reached the new requested value. It can also be seen that for the changes of load from a very light to a heavy value (as shown in Fig. 5) the steer operation reduces to a single switching action, where only  $SW_1$  and  $SW_3$  are turned on until the desired current is reached. Such simplified operation is possible as long as the inductor current can be charged to the new steady state value before a significant change of the capacitor voltage due to the load current occurs. Otherwise, a more advanced control action is required, as described in the following subsection.

# A. Preventing Significant Capacitor Discharge During Inductor Current Steering

As shown in Figs. 2 and 3, during the inductor current steering, the output capacitor is not connected to the inductor. As a result, it discharges through the load that causes a voltage drop. When the load change is significant, this voltage drop cannot be neglected. In order to minimize this variation, a threshold for the maximum allowable voltage dip is set, the output is monitored, and a periodic switching between *steering and boost* operation is activated accordingly.

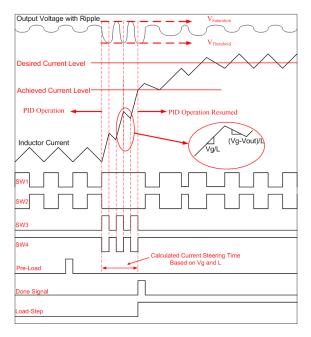

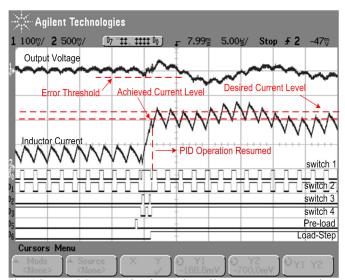

The operation in this mode is illustrated in Fig.6. In the case of light-to-heavy load transient, if the output voltage drops below the threshold ( $V_{out} < V_{Threshold}$ ), the mode control logic momentarily stops the steer operation to charge up the output capacitor back to the desired level by turning on  $SW_1$  and  $SW_4$ . After the voltage is recovered, the logic reestablishes the steering through  $SW_1$  and  $SW_3$ . This allows increasing the inductor current while maintaining the output voltage. Similarly, during a heavy-to-light load transient in order to prevent capacitor discharging beyond the threshold the steer operation is periodically paused and the output capacitor is charged by the inductor by turning off  $SW_5$  and turning on  $SW_4$  (Fig. 4).

Fig.5. Gating signals for different modes of operation.

Fig.6. The converter operation as a boost converter during light-toheavy load transient.

# IV. EXPERIMENTAL SYSTEM AND RESULTS

To verify the operation of the system shown in Fig. 1 an experimental system was built. The 30-W, 3.3-V, 500 kHz power stage is designed for the input voltage ranging between 1.5V and 12V. To compare the performance, a time optimal controller capable of recovering output voltage through a single on-off action, similar to [10], was developed as well.

The experimental results presented in Figs. 7 to 10 show comparisons of the transient responses of both converters and

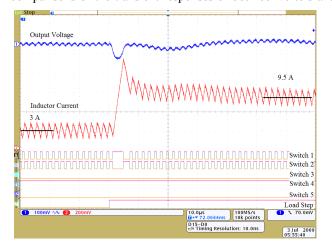

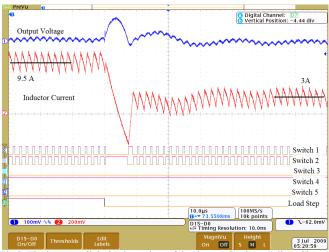

Fig.7. The light-to-heavy load transient of the time-optimal controller-Ch1: output converter voltage (100mV/div); Ch2: inductor current (3.5A/div).

Fig.8. The light-to-heavy load transient of the proposed load-interactive controller– Ch1: output converter voltage (100mV/div); Ch2: inductor current (3.5A/div).

verify superior performance of the load-interactive steeredinductor topology. The waveforms show the comparison for the case when the converter is operating as a buck with a 10V input and 3.3 V output. Fig. 11 and 12 show the converter switching in *steer and boost* operation mode.

Fig. 7 shows the transient response of the time-optimal controller to a 6.5A light-to-heavy load transient. The gating signals of  $SW_1$  and  $SW_2$  depict the action of the time-optimal control during the transient. Fig. 8 shows the response of the load-interactive system. It can be seen that the new system has less than one half of the voltage undershoot for the same load step. Moreover, unlike the time optimal controller, the load-interactive system exposes the inductor to a much smaller peak current preventing possible saturation. The pre-load command that informs the converter prior to the occurrence of the load step is also shown. Based on the pre-load command  $SW_1$  and  $SW_3$  are turned on, to charge up the inductor to the desired level. Once the desired current is achieved the regular

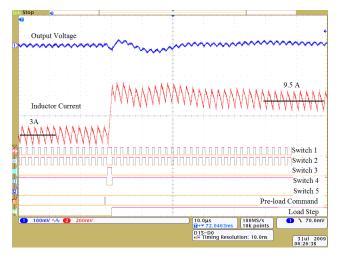

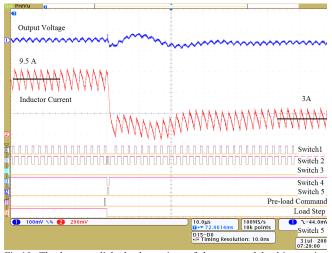

Fig.9. The heavy-to-light load transient of the time-optimal controller- Ch1: output converter voltage (100mV/div); Ch2: inductor current (3.5A/div).

Fig.10. The heavy-to-light load transient of the proposed load-interactive controller– Ch1: output converter voltage (100mV/div); Ch2: inductor current (3.5A/div).

PID operation is resumed and it continues until the next preload command is received.

Figs. 9 and 10 show the transient responses of the timeoptimal controller and that of the proposed load-interactive converter to a 6.5A heavy-to-light load step, respectively. A similar improvement to that for the light-to heavy transient case can be observed. The waveforms of Fig.10 also experimentally verify the operation described in Section II. It can be seen that the steer inductor operation during the heavyto-light load transient is performed at the point of the actual load step. The digital gating signals of  $SW_2$  and  $SW_5$  indicate that the inductor current is driven back to the source until it reaches the desired value.

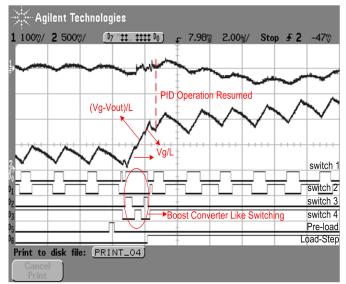

Figs. 11 and 12 show the converter operation in *steer and boost* mode, due to the output voltage drop below threshold voltage. In Fig. 11 it is shown that the inductor current level

Fig.11.Steer and Boost mode of operation- Ch1: output converter voltage (100mV/div); Ch2: inductor current (5A/div).

Fig.12. Boost converter like switching during steer and boost operation– Ch1: output converter voltage (100mV/div); Ch2: inductor current (5A/div).

achieved is below the desired load current level due this operation. Nevertheless, this operation brings the inductor current close to the desired level, while maintaining the output voltage in the acceptable range. Fig. 12 zooms into this operation to show the boost converter like switching. As this operation is taking place during buck mode, when  $SW_1$  and  $SW_4$  conduct to restore the output voltage, the inductor current increases with a slope  $(V_g - V_{out}/L)$  which is lower than the slope during the steer operation  $(V_g/L)$ .

## CONCLUSIONS

A load interactive flexible digitally controlled dc-dc converter with minimized output filter capacitor is introduced. It is shown that by using a modified buck-boost converter, named steered inductor buck-boost, and by improving communication between the converter and its digital load the size of the output capacitor can be drastically reduced. Based on the information about the load current, the inductor current is steered into or out of the capacitor, at a much higher slew rate compared to the conventional designs, minimizing the current provided by the capacitor during load transients. Theoretically, the newly proposed system opens a possibility of designing dc-dc converters such that the output filter capacitor is selected only based on the maximum allowable switching ripple, thus drastically reducing the overall size of the dc-dc converters.

#### REFERENCES

[1] T. Burd, , T. Pering, A.Stratakos and R.Brodersen. "A Dynamic Voltage Scaled Microprosseor System," In *IEEE ISSCC* pp.294-295, Feb 2000.

[2] R. Gonzalez,; B.M Gordon, M.A Horowitz, "Supply and threshold voltage scaling for low power CMOS," *IEEE Jour. Solid-State Circ.*, vol, 32, no. 8, pp 1210-1216, August 1997.

[3] M. Miyazaki, M. Ono, G. Hattori, T. Shiozawa, K. Uchiyama, K. Ishibashi, "A 1000-MIPS/W microprocessor using speed adaptive threshold-voltage CMOS with forward bias," In *IEEE ISSCC* pp.420-425, Feb 2000.

[4] Kuroda, T. Fujita, T. Mita, S. Nagamatsu, T. Yoshioka, S. Suzuki, K. Sano, F. Norishima, M. Murota, M. Kako, M. Kinugawa, M. Kakumu, M. Sakurai, "A 0.9-V, 150-MHz, 10-mW, 4 mm2, 2-D discrete cosine transform core processor with variable threshold-voltage (VT) scheme," *IEEE Jour. Solid-State Circ.* Vol.31, no.11, Nov 1996, pp 1770-1779.

[5] A.P. Chandrakasan, R.W. Brodersen, "Minimizing Power consumption in Digital CMOS circuits," *Proc. IEEE* vol. 83, NO 4, April 1995, pp. 498 – 523.

[6] Kao, J.T., Miyazaki, M., and A.P. Chandrakasan, "A 175-mV Multiply-Accumulate Unit Using an Adaptive Supply Voltage and Body Bias Architecture," *IEEE Jour. Solid-State Circ.* vol. 37, Nov.2002, pp. 1545 – 1554.

[7] "Intel VRM 11.1 Design Guideline," Available online at http://www.intel.com/technology/itj/index.htm.

[8] Z. Lukić, Z. Zhao, A.Prodić, and D. Goder "Digital Controller for Multi-Phase DC-DC Converters with Logarithmic Current Sharing," in *Proc. IEEE PESC*, 2007, June 2007.

[9] O. Trescases, G. Wei, A. Prodić, W.T. Ng, K. Takasuka, T. Sugimoto, and H. Nishio "A Digital Predictive On-Line Energy Optimization Scheme for DC-DC Converters," in *Proc. IEEE APEC Conf*, March 2007.

[10] Z. Zhao and A. Prodić, "Continuous-time digital controller for high frequency dc–dc converters," *IEEE Trans. Power Electron.*, vol. 23, no.2, pp. 564–573, Mar. 2008.

[11] Z.Yousefzadeh, A. Babazadeh, B. Ramachandran, E.Alarcón, L.Pao, D. Maksimovic "Proximate Time-Optimal Digital Control for Synchronous

Buck DC–DC Converters," *IEEE Trans. Power Electron.*, vol. 23, no.2, pp. 564–573, July. 2008.

[12] A. Stupar, Z. Lukić, and A. Prodić, "Digitally-Controlled Steered-Inductor Buck Converter for Improving Heavy-to-Light Load Transient Response," in *Proc. IEEE PESC conf*, 2008.

[13] Robert W. Erickson and Dragan Maksimović, "Fundamentals of Power Electronics," Second Edition, New York: Springer Science+Business Media, 2001.

[14] "International Technology Roadmap for Semiconductors 2005 Edition Executive Summary," pp. 81-82. Available online at <u>http://www.itrs.net/Links/2005ITRS/ExecSum2005.pdf</u>

[15] P. Henry , "New Advances in Portable Electronics," in *APEC Plenary Session* , March 2009.

[16] R. Paul, L. Corradini, D. Maksimović, " $\Sigma$ - $\Delta$  Modulated Digitally Controlled Non-Inverting Buck-Boost Converter for WCDMA RF Power Amplifiers," in *Proc. IEEE APEC Conf*, March 2009.

[17] A. Prodić and D. Maksimović, "Digital PWM Controller and Current ] ator for a Low-Power Switching Converter," *in Proc., IEEE Computers in Power Electronics Conference (IEEE COMPEL)*, July 2000, pp. 123-128.